不了解DRAM吗? 1分钟内获取DRAM的工作原理!

1. DRAM简介DRAM的英文全称是“ Dynamic RAM”,它被翻译成中文,称为“ Dynamic RAM”。 DRAM只能保留短时间的数据。

为了保留数据,必须定期刷新DRAM。如果不刷新存储单元,则数据将丢失。

DRAM用于常规数据访问。我们经常说存储器有多大,主要是指DRAM的容量。

DRAM的所有基本单元均由晶体管和电容器组成。请看下图:上图只是DRAM基本单元的结构示意图:电容器的状态决定DRAM单元的逻辑状态是1还是0,但电容器的特性是使用也是其缺点。

电容器可以存储一定数量的电子或电荷。在数字电子设备中,充电电容器被认为是逻辑1,而“空”电容器被认为是逻辑1。

电容器为0。电容器不能长时间保持存储的电荷,因此需要定期刷新存储器以保持临时存储的数据。

电容器可以通过电流充电-当然,该电流有一定的限制,否则电容器将被击穿。同时,电容器的充电和放电需要一定的时间。

尽管在存储器的基本单元中电容器的时间非常短,仅约0.2-0.18微秒,但在此期间无法访问存储器。根据DRAM制造商的一些数据,必须至少每64ms刷新一次内存,这意味着有1%的内存被刷新。

内存的自动刷新对于内存制造商而言不是问题,但关键是在读取存储单元时保持内存内容不变-因此在每次读取操作后必须刷新DRAM单元:执行返回操作写操作操作,因为读操作还将破坏内存中的电荷,这意味着存储在内存中的数据是破坏性的。因此,不仅需要每64ms刷新一次内存,而且还需要在每次读取操作之后刷新一次。

当然,这增加了访问操作的周期,等待时间也更长。 SRAM,静态RAM不存在刷新问题。

SRAM的基本单元包括4个晶体管和2个电阻器。它不使用电容器充电和放电的特性来存储数据,而是使用置位晶体管的状态来确定逻辑状态-与CPU中的逻辑状态相同。

读操作对SRAM没有破坏性,因此SRAM不存在刷新问题。 SRAM不仅可以以比DRAM高的时钟频率运行,而且具有比DRAM短得多的延迟。

SRAM只需要2到3个时钟周期即可从CPU缓存中加载所需的数据,而DRAM则需要3到9个时钟周期(此处我们忽略了CPU,芯片组和内存控制电路之间的信号传输时间)。 2.基本原理DRAM由晶体管和小容量f电容存储单元组成。

每个存储单元都有一个小的蚀刻晶体管,该晶体管通过一个小电容器的电荷维持存储状态,即导通和截止。电容类似于小型可充电电池。

可以用电压表示它为1,在放电后,它表示为0,但是已充电的电容器会因放电而失去电荷,因此必须通过新的电荷对其进行连续刷新。下图显示了标准DRAM的结构框架图,与SRAM不同,标准DRAM的地址线分为两组,以减少输入地址引脚的数量并提高封装效率。

尽管在标准DRAM结构中,可以通过安排地址方法来减少输入地址引脚的数量以减少输入,但是在这种情况下,标准DRAM存储单元的时钟控制将变得更加复杂,并且会影响操作速度。为了满足高速DRAM应用的需求,通常使用单独的地址输入引脚来降低时钟控制的复杂性并提高操作速度。

DRAM控制器提供行地址选通-M(行地址选通)和列地址选通CAS(列地址选通)以锁定行地址和列地址。如图所示,标准DRAM的引脚为:地址:分为两组,行地址引脚,列地址引脚;地址控制信号引脚:RAS和CAS;写使能信号:WRITE;数据输入/输出引脚;电源引线脚。

上面是“ DRAM”。该编辑器带来的相关内容。

通过这篇文章,我。

最新资讯

-

200W厚膜无感功率电阻在精密电子设备中的关键作用

200W厚膜无感功率电阻的技术定位与市场价值随着电子设备向小型化、高集成度发展,200W厚膜无感功率电阻凭借其紧凑体积与优异电气性能,成为中等功...

-

200W厚膜无感功率电阻在精密控制电路中的关键作用

200W厚膜无感功率电阻的技术突破与工程价值随着现代工业自动化水平的提升,对功率电阻的精度、响应速度和电磁兼容性提出了更高要求。200W厚膜无感...

-

250W厚膜无感大功率电阻的性能优势与应用解析

250W厚膜无感大功率电阻的核心特性在高功率电子系统中,250W厚膜无感大功率电阻因其卓越的热稳定性和低电感设计,成为工业级电源、逆变器和电机控...

-

如何选择合适的200W厚膜无感功率电阻?技术参数与选型指南

200W厚膜无感功率电阻选型关键指标在实际应用中,正确选择200W厚膜无感功率电阻至关重要。以下是必须关注的技术参数:1. 额定功率与降额使用虽然标...

-

200W厚膜无感功率电阻的性能优势与应用场景深度解析

200W厚膜无感功率电阻的核心优势200W厚膜无感功率电阻因其卓越的散热性能和高稳定性,广泛应用于工业电力系统、新能源设备及高端电子仪器中。其核...

-

如何选择合适的150W厚膜无感功率电阻?实用指南

选购150W厚膜无感功率电阻的关键考量因素在众多功率电阻中,150W厚膜无感型号因其高性能而备受青睐。然而,正确选型需综合考虑多个参数,以确保系...

-

150W厚膜无感功率电阻的性能优势与应用解析

150W厚膜无感功率电阻的核心特性150W厚膜无感功率电阻是一种专为高功率、高稳定性设计的电子元件,广泛应用于工业电源、逆变器、电机控制及大功率...

-

SOT227 120W功率电阻在新能源设备中的关键作用

SOT227 120W功率电阻在新能源系统中的价值随着新能源产业快速发展,尤其是光伏、风电与储能系统的普及,对高可靠性、高效率功率元器件的需求日益增...

-

SOT227 120W厚膜无感功率电阻详解:性能优势与应用场景解析

SOT227 120W厚膜无感功率电阻核心特性SOT227封装的120W厚膜无感功率电阻是一种专为高功率、高稳定性应用设计的电子元件。其采用厚膜技术制造,具备优异...

-

深入理解TO-247 100W厚膜电阻:从选型到应用的最佳实践指南

TO-247 100W厚膜电阻的技术参数与应用要点全解析随着电力电子设备向更高功率密度和更紧凑结构发展,对关键元器件的性能要求日益严苛。本文将围绕TO-...

最新资讯

-

iPhone12 mini销量平均,降价是唯一的出路

2020年,苹果公司发布的iPhone 12系列手机虽然存在各种问题,但并未阻止iPhone 12系列在全球市场上的畅销。在新机器的帮助下,苹果公司在年度销售榜上已...

-

三星正在与AMD合作开发Exynos处理器

苹果公司宣布其Mac版M1处理器使许多人对计算机上运行的Exynos,麒麟和Snapdragon处理器产生了兴趣。高通公司目前拥有用于计算机的基于Arm的处理器,但该...

-

Galaxy S21 Plus可能很快会赢得另一种颜色选择

GalaxyS21Plus可能很快会在三星的官方虚拟商店中出售另一种颜色选择。正如荷兰门户网站NieuweMobiel的人所发现的那样,这家韩国公司的本地页面已经有“中...

-

PC和Android移动设备更好地兼容

Windows 10移动版陷入困境后,微软将重点更多地放在在Android生态系统(例如SurfaceDuo双屏智能手机)中部署自己的软件和服务。为了使PC与Android移动设备更...

-

关于电力系统中谐振过电压的产生和解决方案

什么是谐振过电压?谐振过电压是指电力系统中的某些电感和电容元件在系统运行或出现故障时会形成各种振荡电路。在某种能源的作用下,会发生串联...

-

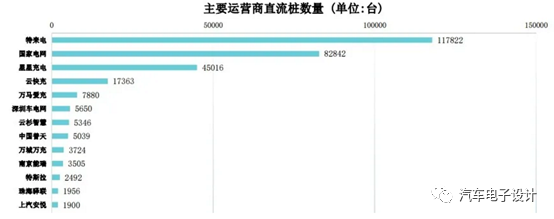

特斯拉快速充电网络的扩展速度有多快?

我阅读了有关数百人大的一些信息。由于云广播,我搬到了中英论坛。 16号的内容尚未上传。这是一件非常有趣的事情。由于特斯拉去年在中国销售了近...

-

三星Galaxy M62电池容量已通过联邦通信委员会颁发的证书

三星Galaxy M62电池容量已通过联邦通信委员会颁发的证书进行了披露。该公司为用户提供具有高电池容量的中档机型,Galaxy M62机型的电池也将引起关注。...

-

使用断路器锁时,您需要摆脱这六个不良习惯

长时间使用后,家里的断路器锁很快就会被破坏。实际上,这仅仅是因为您在应用程序中有六个不良习惯。然后家里的断路器锁很容易销毁,所以在保养...

-

一次和二次熔断柱断路器在电源电路中的应用

主熔断器熔断器和辅助熔断器断路器在电源电路中的应用着眼于低故障率和非常低的强制关机率。实际上,一次和二次熔断式极点断路器的老产品已经在...

-

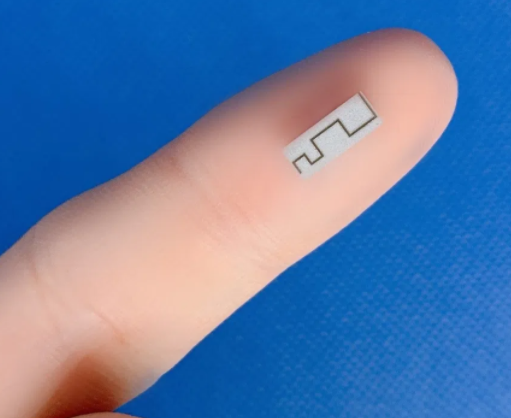

东芝已交付世界上最小的蓝牙低功耗模块

东芝已经开发出他们所谓的世界上最小的蓝牙低功耗模块。该模块使用公司专有的屏蔽封装(SASP)技术缝隙天线。东芝已于1月15日开始发货该模块的样品...

13510435585

服务热线:13510435585

联系电话:0797-4282799

公司邮箱:sales@tonevee.com

公司地址:江西省赣州市定南县良富工业区电子产业区5栋

13510435585

13510435585